디지털 시그널)

1. 미분 불가능 포인트가 많다.

2. 그래프상으로도 보면 기울기가 무한대인 즉 기울기를 구할 수 없는 포인트가 있다.

디지털 <--> 아날로그

아날로그 시그널)

1. 연속적이며 미분 가능하다.

2. 부드러운 그래프이다.

디지털 신호에서,

pid제어때, 오버 슈팅이 생길 수 있다. 관성 때문에 궁상떨어서 뜨는 현상

(생김새는 막 뾰족하게 심장박동체크한느것처럼)

이유: 전압을 급격하게 바껴서(아날로그 신호에서)

suddenly change 즉 갑작스러운 변화는 전자 세계에서도 표현을 못한다.

샘플링 레이트를 낮게 잡으면 정보손실이 크다.

시그널이 가지고있는 성분 중에 고주파 성분이 별로 없으면 정보 손실은 별로 없다.

반대로 고주파 성분이 많은 시그널에서는 샘플링 레이트를 낮게 잡으면 정보 손실이 크다.

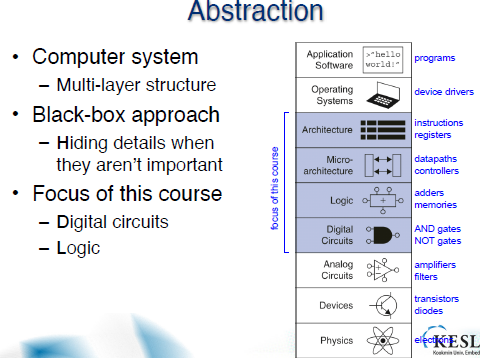

Digitization : 양자화를 통해 변화하는 실수량을 디지털화를 통해 0과 1로 표현하는 것이다.

세상에 있는 모든 정보는 아날로그 신호이다. 하지만 왜 디지털 신호로 바꿀로 할까? 최적화되어있기 때문이다.

사람이 생각하는 표현이나 생각을 논리로 표현하는 것이다. 이산수학 or 대수학

1. AND , 2. OR , 3. NOT

첫 번째로 등장하는 것은 ASIC(Application-Specific-Integrated-Cirkit)이다.

ASIC : 미리 칩이 수행하는 일을 정의를 하고, 그것만 수행하는 전용 칩

- 특정 작업만 하게 되어있어서 성능은 최적화되어있기 때문에 고성능 확보

- 비싸다.

AISC을 단점을 보안한 디바이스는 없나요? PLD라는 게 있다.

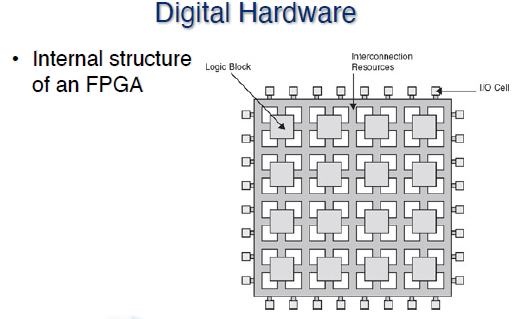

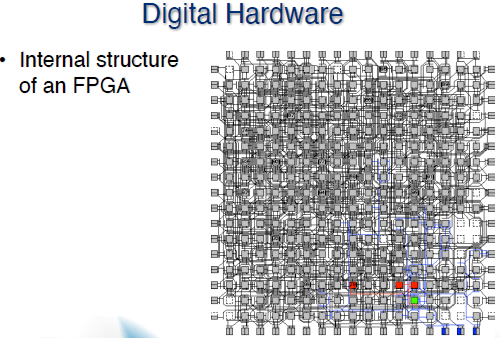

어떻게 쓰일지 모르게 때문에, and or not로직들로 충분히, 많게 구성된 판이다.

FPGA는 PLD의 한 부분이다.

FPGA보다 더 친숙한 즉 C++, 파이썬 등 프로그래밍 언어로 구현 가능한 것은 마이크로프로세서다.

하드웨어 디자인의 관점에서 FPGA는 결정이 되어 있지 않지만(and or not 표준 게이트만 넣어놨을 뿐),

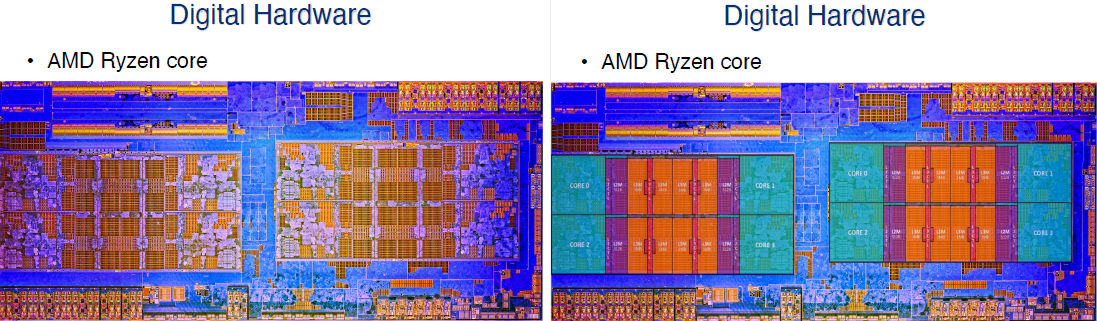

마이크로프로세서는 어떤 특정 기능을 수행할 수 있는 하드웨어를 만들어놨다.(cpu)

최종 정리!

Digital Circuits을 가지고 Architecture(Microprocessor)의 발전과정을 보았다!!

최종 질문?

디지털 로직을 만드는데 크게 3가지 방법으로 분류되는데,

1. ASIC : 특정 로직에 최적화된 '이 로직만 수행할 거야!' 이 관점에서 설계된 로직

2. FPGA : 나중에 어떤 로직을 구동시킬지 모르겠지만, 일단 하드웨어로 구현할 거야! (현장에서 올렸다, 내렸다,

변경했다, 프로그래밍 가능한 로직)

3. Microprocessor : 컴퓨터에서 프로그래밍하는 로직

ASIC과 FPGA의 차이 (2가지의 관점)

1. 칩당 비용

동일한 로직을 만들 때는 ASIS보다 FPGA가 더 싸다.

2. 시제품을 만들어서 검증하기 위한 제작비용

FPGA는 새로운 제품을 잘되는지 검증하는데 소량을 살 수가 있다. (프로토타입: 시제품 관점에서)

ASIC은 칩당 가격이 FPGA보다 싸지만, 소량으로 살수가 없다.

ex) Asic 웨입 한 장에 1000만 원이고 그 안에 칩은 1000개가 들어간다 가정하에(칩은 개당 1만 원),

내가 칩이 10개만 필요해도 1000만 원이 들어간다. (동일 로직 1000개가 오기 때문에)

반대로, FPGA는 칩이 개당 5만 원인데 10개만 필요하면 50만 원만 쓰면 된다.

'Study > Digital Logic Design' 카테고리의 다른 글

| 논리회로설계 3-2 (0) | 2022.03.22 |

|---|---|

| 논리회로설계 3-1 (0) | 2022.03.22 |

| 논리회로설계 2-2 (0) | 2022.03.21 |

| 논리회로설계 2-1 (0) | 2022.03.21 |

| 논리회로설계 1-1 (0) | 2022.03.21 |